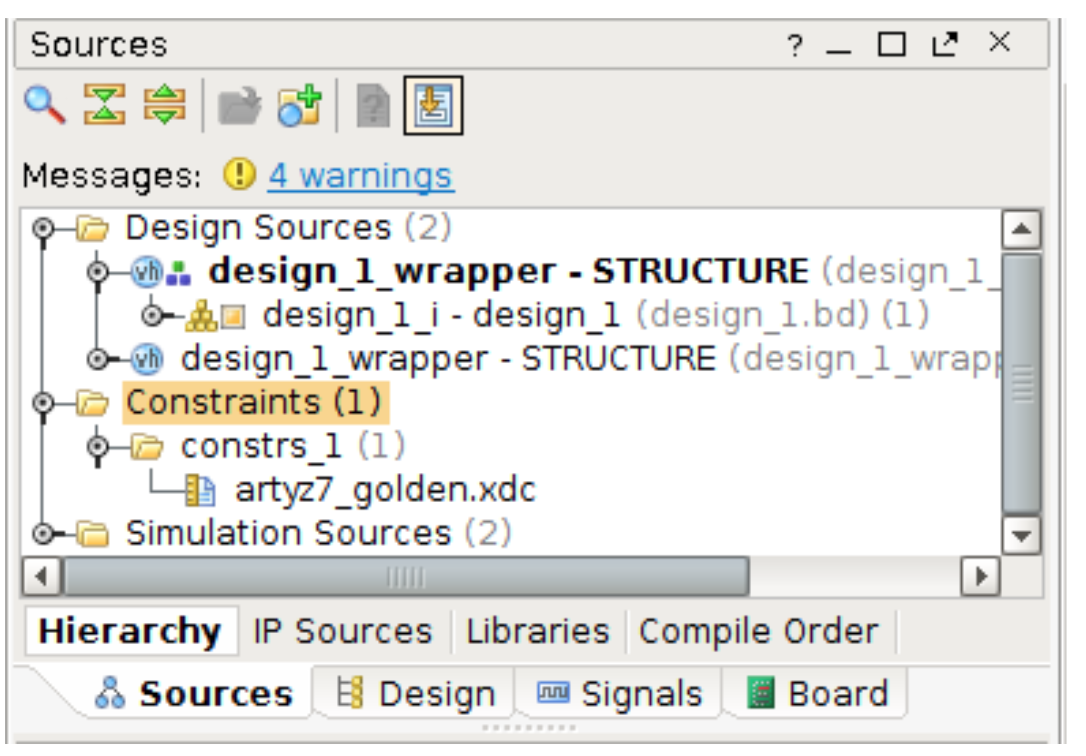

Now we have to map the signals exported in HDL wrapper to the physical pins of the board. In the following we listed the changes that we have done in the artyz7_golden.xdc file located in Constraints directory under source window.

Finally we are ready to generate the bitstream!

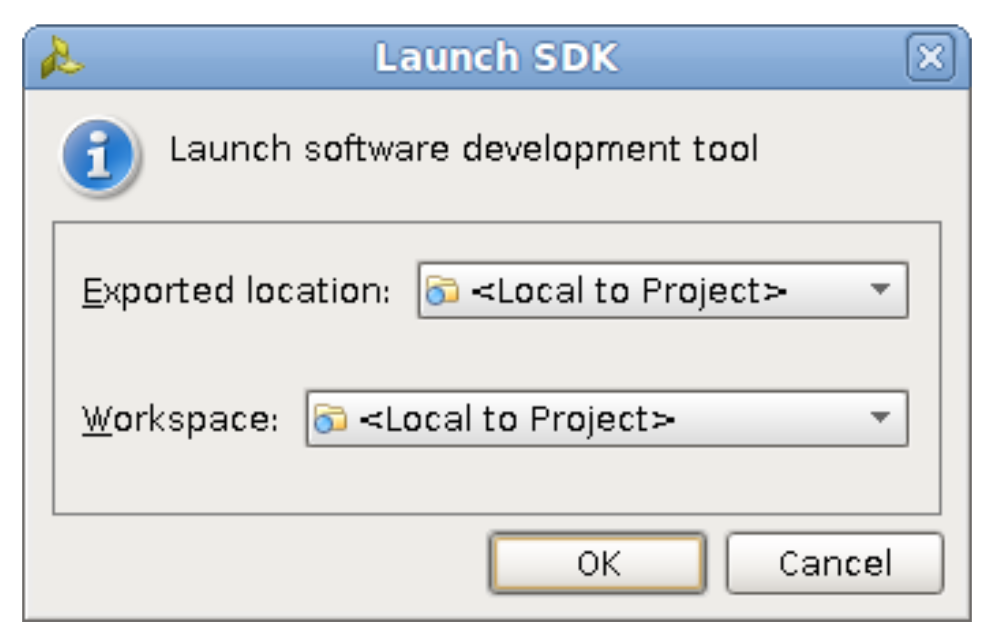

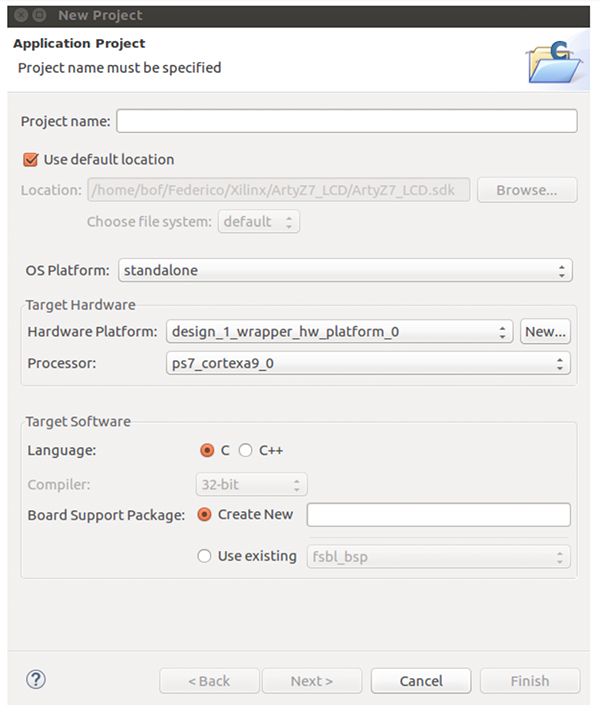

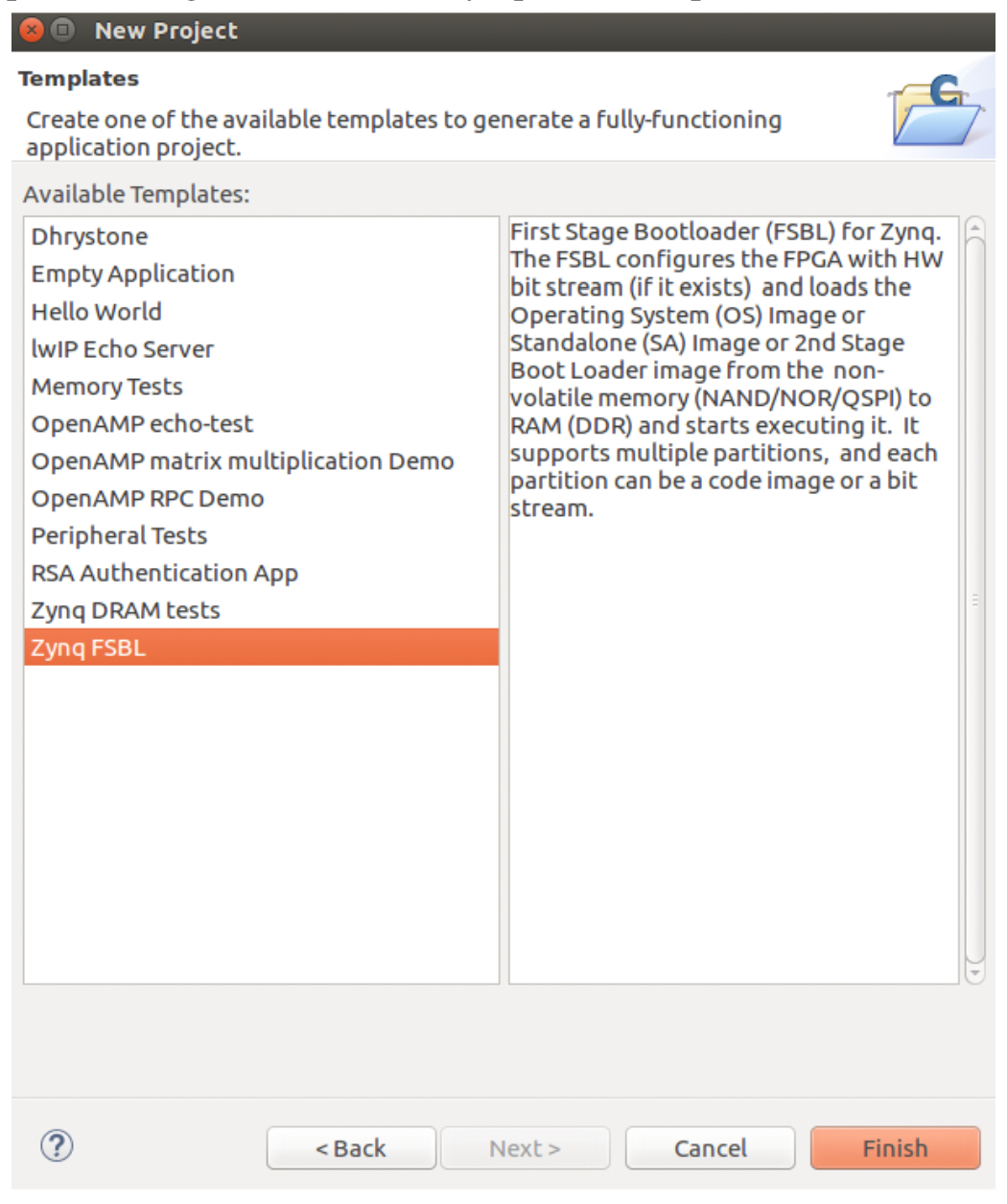

While bitstream is performing, we can launch SDK tool.

##Pmod Header JA

set_property -dict { PACKAGE_PIN Y18 IOSTANDARD LVCMOS33 } [get_ports { spi_0_io0_io }]; #IO_L17P_T2_34 Sch=JA1_P

set_property -dict { PACKAGE_PIN Y19 IOSTANDARD LVCMOS33 } [get_ports { spi_0_io1_io }]; #IO_L17N_T2_34 Sch=JA1_N

set_property -dict { PACKAGE_PIN Y16 IOSTANDARD LVCMOS33 } [get_ports { spi_0_sck_io }]; #IO_L7P_T1_34 Sch=JA2_P

set_property -dict { PACKAGE_PIN Y17 IOSTANDARD LVCMOS33 } [get_ports { spi_0_ss_o }]; #IO_L7N_T1_34 Sch=JA2_N

set_property -dict { PACKAGE_PIN U18 IOSTANDARD LVCMOS33 } [get_ports { spi_io0_io }]; #IO_L12P_T1_MRCC_34 Sch=JA3_P

set_property -dict { PACKAGE_PIN U19 IOSTANDARD LVCMOS33 } [get_ports { spi_io1_io }]; #IO_L12N_T1_MRCC_34 Sch=JA3_N

set_property -dict { PACKAGE_PIN W18 IOSTANDARD LVCMOS33 } [get_ports { spi_sck_io }]; #IO_L22P_T3_34 Sch=JA4_P

set_property -dict { PACKAGE_PIN W19 IOSTANDARD LVCMOS33 } [get_ports { spi_ss_o }]; #IO_L22N_T3_34 Sch=JA4_N ##Pmod Header JB

set_property -dict { PACKAGE_PIN Y14 IOSTANDARD LVCMOS33 } [get_ports { spi_0_ss1_o }]; #IO_L8N_T1_34 Sch=JB1_N

set_property -dict { PACKAGE_PIN W14 IOSTANDARD LVCMOS33 } [get_ports { spi_0_ss2_o }]; #IO_L8P_T1_34 Sch=JB1_P

set_property -dict { PACKAGE_PIN T10 IOSTANDARD LVCMOS33 } [get_ports { spi_0_ss_t }]; #IO_L1N_T0_34 Sch=JB2_N